## QUADRUPLICADOR DE FREQUÊNCIAS ATIVO: 1/4 GHz

Fatima S. Correra e Edmar Camargo

Laboratório de Microeletrônica da EPUSP

Caixa Postal 8174 - CEP 01051 - São Paulo

### RESUMO

Apresentam-se neste trabalho os critérios de projeto e a realização experimental de um quadruplicador de frequências a transistor MESFET, constituído por dois dobradores de frequência em cascata. O protótipo projetado apresenta ganho de multiplicação de 10 dB de 1 GHz para 4 GHz, fornecendo  $+ 10 \pm 0,5$  dBm de potência de saída numa banda de frequência de 575 MHz.

### INTRODUÇÃO

O recente desenvolvimento dos circuitos integrados monolíticos de microondas em Arseneto de Gálio aumentou o interesse em multiplicadores de frequências ativo a transistor MESFET. Este tipo de multiplicador de frequências pode ser prontamente integrado em "chips" multifunção contendo outros circuitos a MESFET, sem aumento da complexidade das etapas tecnológicas de fabricação. Desse modo os osciladores a transistor MESFET podem ser associados a multiplicadores de frequência, obtendo-se fontes de sinal a transistor operando até a faixa de ondas milimétricas, integradas em um bloco monolítico de semicondutor.

Este trabalho apresenta o projeto de um multiplicador de frequências ativo 1/4 GHz, utilizando tecnologias de circuito impresso e filme fino e componentes discretos. Durante o projeto procurou-se investigar a possibilidade de obter ganho de multiplicação, potência de saída e faixa de frequências compatíveis com aplicações em sistemas de comunicação. As discussões sobre as características do multiplicador visando sua integração em sistemas e as considerações de projeto foram mantidas gerais, podendo ser aplicadas a multiplicadores construídos por tecnologias diferentes e a outras faixas de frequência, até o extremo superior da banda X.

### CONSIDERAÇÕES DE PROJETO

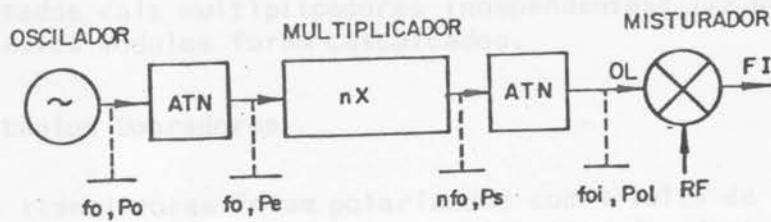

Em sistemas de comunicação o multiplicador de frequências é utilizado em conversores de recepção e/ou transmissão. Sua entrada é o sinal de frequência  $f_o$  e potência  $P_o$ , gerado pelo oscilador, e sua saída é a harmônica  $n f_o$  e potência  $P_s$  que é conectada à porta "oscilador local" do misturador. Conforme ilustrado na Figura 1, a interconexão destes circuitos deve ser feita intercalando-se atenuadores de forma a minimizar a interação entre eles.

Para esta aplicação o multiplicador de frequências deve operar em uma banda de frequências de 10% e níveis de potência de entrada e saída compatíveis com os circuitos aos quais é conectado.

Figura 1 - Aplicação de multiplicador de frequências ativo em sistemas de comunicação

No presente projeto, o oscilador fornece um sinal de 1 GHz e + 10 dBm de potência. A porta "oscilador local" do misturador deve ser bombeada com um sinal de 4 GHz e potência entre + 7 e + 10 dBm. Considerando-se atenuadores de no mínimo 3 dB, obtiveram-se as especificações apresentadas na Tabela I. Atenuadores com maiores valores de atenuação poderão ser utilizados dependendo do desempenho do multiplicador.

|                                  |                 |

|----------------------------------|-----------------|

| Frequência de entrada ( $f_o$ ): | 925 a 1050 MHz  |

| Frequência de saída ( $n f_o$ ): | 3700 a 4200 MHz |

| Potência de entrada ( $P_e$ ):   | $\leq +7$ dBm   |

| Potência de saída ( $P_s$ ):     | $\geq +10$ dBm  |

Tabela I - Especificações do multiplicador de frequências

#### PROJETO DO MULTIPLICADOR DE FREQUÊNCIAS

O objetivo do projeto foi atender às especificações apresentadas no item anterior através de um circuito simples, de fácil ajuste e baixo custo, visando posterior industrialização do protótipo. Duas filosofias de projeto podem ser adotadas para se realizar um multiplicador de frequências por 4: a multiplicação direta de  $f_o$  para 4  $f_o$  ou a multiplicação em duas etapas -  $f_o$  para 2  $f_o$  seguida de 2  $f_o$  para 4  $f_o$ . A primeira opção pode ser realizada com transistor MESFET "dual-gate" realimentado<sup>1</sup>. A segunda emprega dois transistores MESFET comuns e foi adotada por apresentar melhor desempenho em banda de frequência e utilizar circuitos mais simples.

O transistor empregado foi o NE 21889 fabricado pela NEC. Trata-se de um dispositivo de baixo ruído e baixo custo, que operando como amplificador em 4 GHz fornece 17 dB de ganho e 50 mW de potência no ponto de 1 dB de compressão.

Estudos realizados anteriormente<sup>2</sup> sobre o comportamento não-linear dos transistores MESFET revelam que seu desempenho em multiplicadores de frequências depende do ponto de polarização, da impedância e do nível de sinal do gerador e da terminação de saída. A forma mais eficiente de obter-se um dobrador de frequências consiste na exploração da não-linearidade da transcondutância do MESFET,  $g_m$ , devendo-se para tanto polarizar o transistor próximo ao corte. A terminação de saída para a máxima modulação de  $g_m$  corresponde a um curto circuito no plano do dreno na frequência fundamental. Nesta condição, a condutância de saída,  $g_d$ , pode ser aproximada por seu valor em pequenos sinais. A impedância não-linear resultante na entrada deve ser conjugadamente casada com a impedância do gerador na frequência fundamental. O projeto foi realizado em duas etapas que serão descritas a seguir. Na primei

ra foram projetados dois multiplicadores independentes: 1/2 GHz e 2/4 GHz. Na segunda etapa estes módulos foram cascataados.

### Estágios Dobradores

Os transistores foram polarizados com 4 volts de tensão de dreno e -1 volt de porta, próximo ao corte. Os circuitos de adaptação de impedância de entrada dos dobradores foram projetados atendendo ao compromisso entre maximização de potência entregue ao transistor e estabilidade dos circuitos. Assumiu-se que na faixa de projeto o transistor utilizado é unilateral, de modo que sua impedância de entrada independe da terminação de saída e do comportamento não linear de  $g_m$ . Na entrada do transistor do primeiro dobrador utilizou-se um indutor série que ressoa parcialmente a capacitação porta-fonte,  $C_{gs}$ . No segundo dobrador a entrada do transistor foi parcialmente casada para 50 ohms através de uma linha de transmissão série e um toco em aberto.

Os circuitos de adaptação de impedância de saída foram projetados de modo a impor simultaneamente no dreno um curto-círcuito para a frequência fundamental e 50 ohms para a segunda harmônica. No dobrador 1/2 GHz esta condição de circuito foi obtida por meio de um toco em aberto de  $\lambda/4$  na frequência fundamental conectado junto ao dreno. No dobrador 2/4 GHz utilizou-se como circuito de saída um filtro passa-faixa de 4 seções de microlinhas acopladas, que apresenta 1 dB de perda na faixa de 3,7 a 4,2 GHz. O curto-círcuito no dreno na frequência fundamental, 2 GHz, foi obtido inserindo-se um trecho de linha de transmissão de  $50\Omega$  e comprimento adequado entre o transistor e o filtro. Este filtro tem ainda a função de rejeitar as harmônicas indesejáveis na saída do dobrador.

Cada dobrador foi caracterizado individualmente, obtendo-se: 6 dB de ganho de multiplicação de 1 para 2 GHz com 0 dBm de potência de entrada, e 6 dB de ganho de multiplicação de 2 para 4 GHz com +6 dBm de potência de entrada.

### Multiplicador 1/4 GHz

De um modo geral os efeitos resultantes da conexão de dois circuitos fortemente não-lineares em cascata só podem ser avaliados através de um programa de análise não-linear dedicado. Além disso, não existe na literatura critérios para o projeto otimizado deste tipo de circuito. No projeto em questão, a integração dos dois dobradores é simplificada porque o nível de potência na entrada do 2º dobrador não ocasiona condução do diodo porta-fonte, podendo-se considerar que a impedância de entrada do mesmo é linear. Logo, o fato de substituir a carga de 50 ohms do primeiro estágio por uma impedância complexa linear não altera significativamente o comportamento não-linear, o qual é imposto pelo curto-círcuito no dreno na frequência fundamental. Este fato foi comprovado através de simulação não-linear em programas de computação especialmente desenvolvidos<sup>2</sup>. No entanto, o ganho de multiplicação global deverá sofrer alterações devido ao elevado nível das reflexões entre estágios, que influem na amplitude da tensão sobre o capacitor  $C_{gs}$  do segundo estágio de multiplicação.

Na falta de uma infra-estrutura computacional adequada ao projeto, os dois estágios foram cascataados como se estivessem adaptados para 50 ohms. Os elementos de circuito entre estágios foram então experimentalmente ajustados com os objetivos de otimizar ganho de multiplicação e banda de operação. Os ensaios experimentais demonstraram necessidade de se acrescentar elementos de circuito em relação aos estágios independentes. Verificou-se porém que o circuito tornou-se mais sensível aos níveis de potência e que houve redução da faixa dinâmica de operação devido à interação entre os dois

estágios dobradores.

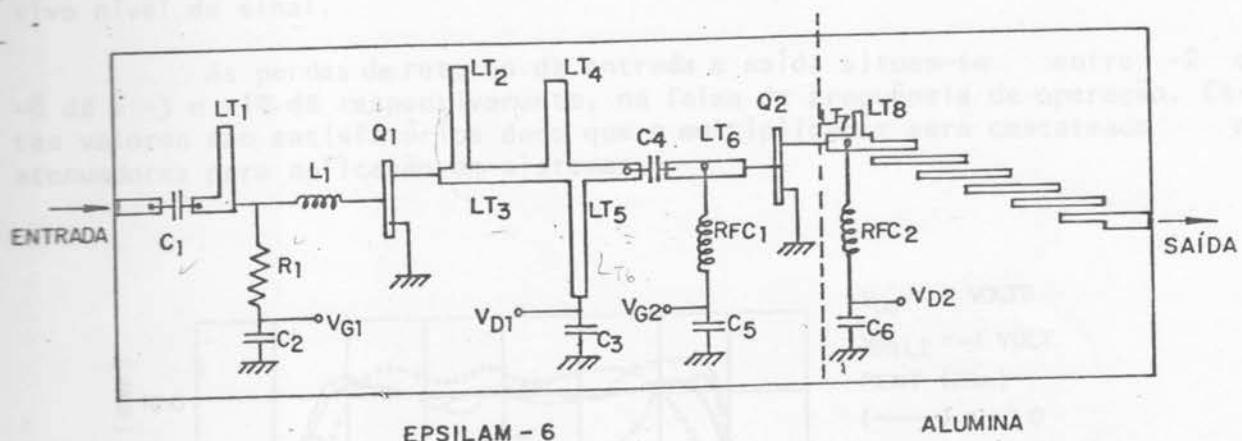

## DESCRICAÇÃO DO CIRCUITO

O circuito elétrico equivalente do multiplicador de frequência é apresentado na Figura 2. O sinal de entrada, 1 GHz, é alimentado à porta do primeiro transistor Q1, através do toco em aberto LT1 e da indutância L. A saída de Q1 encontra-se conectado o toco em aberto LT3 de comprimento  $\lambda/4$  em 1 GHz. A segunda harmônica gerada alimenta Q2 através de LT5 e LT6 os quais foram ajustados experimentalmente. O filtro com linhas acopladas está conectado ao dreno de Q2 através da linha série TL8, que controla a terminação reativa de saída em 2 GHz. O toco em aberto LT9 é um ajuste adicional do circuito de saída, empregado para melhorar a planicidade do ganho de multiplicação na faixa de operação.

O filtro de polarização da porta Q1 é constituído pelo filtro R1C2 passa-baixa e a polarização de dreno é realizada através de LT6 e C3. O transistor do segundo estágio de multiplicação é polarizado através de "chockes" de RF em série com capacitores multicamadas.

Figura 2 - Circuito elétrico equivalente do quadruplicador de frequências

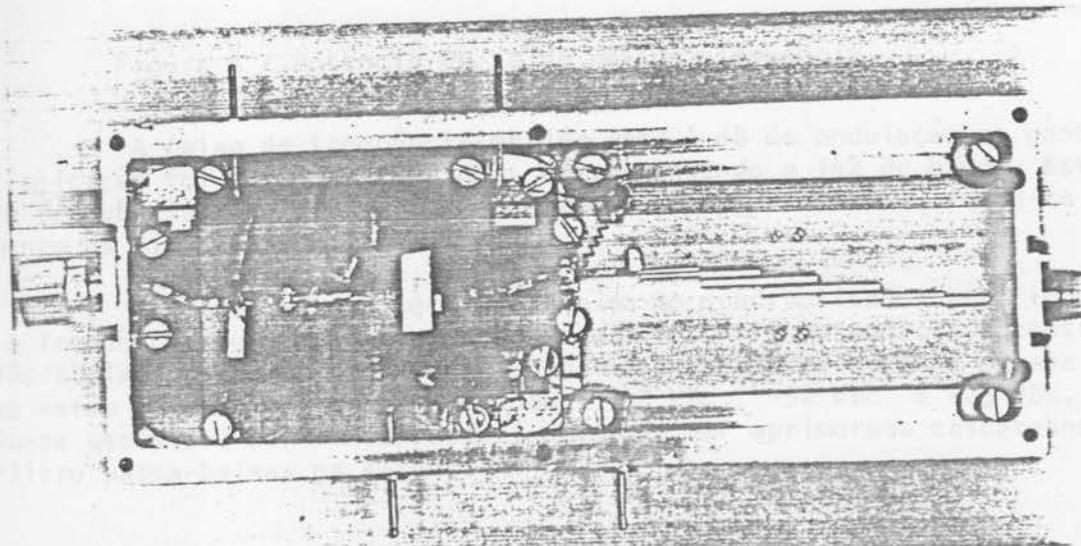

Com exceção do filtro de saída que foi construído por técnica de filme fino sobre substrato de alumina, os demais circuitos foram montados sobre substrato flexível - Epsilam 6. O circuito completo ocupa uma área de 10,2 cm x 3,3 cm, tendo sido montado em caixa de alumínio e conectado a transições microlinhas/SMA como ilustrado na foto da Figura 3.

Figura 3 - Foto do protótipo do quadruplicador de frequência

## RESULTADOS EXPERIMENTAIS

O quadruplicador foi caracterizado para diferentes níveis de sinal de entrada através da medida do ganho de multiplicação e perda de retorno de entrada em analisador de circuitos escalar e da perda de retorno de saída determinada por medidas indiretas<sup>3</sup>. Determinou-se ainda o nível de sinais espúrios na saída através de analisador de espectro.

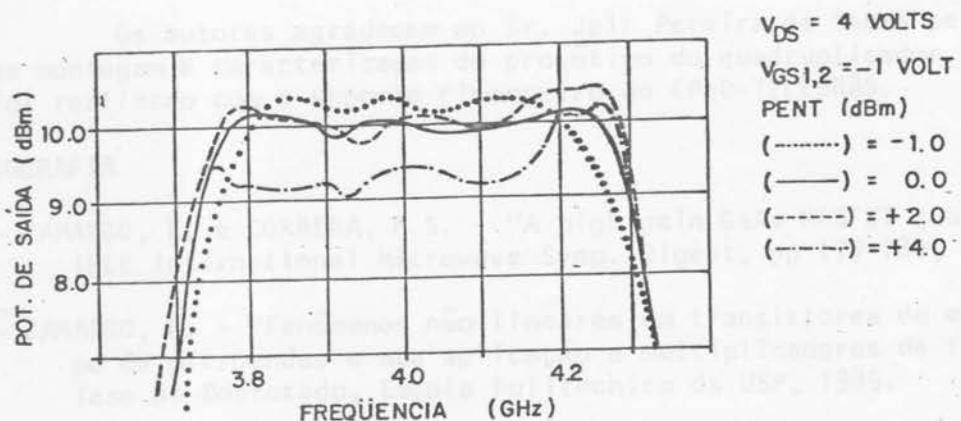

A Figura 4 apresenta a potência de saída em função da frequência, tendo como parâmetro a potência de entrada. Verifica-se que o multiplicador opera saturado, de modo que variando-se a potência de entrada entre -1 e +3 dBm a potência de saída praticamente não se altera. Este comportamento é particularmente interessante para o caso de integração do oscilador e do quadruplicador na forma de um circuito monolítico, pois torna o desempenho do conjunto relativamente insensível a variações de potência do oscilador local. Verifica-se também que para potência de entrada de +4 dBm há uma queda na potência de saída. Este efeito é causado por perdas resistivas na entrada do segundo dobrador, devido à condução do diodo porta-fonte submetido a excessivo nível de sinal.

As perdas de retorno de entrada e saída situam-se entre -2 e -8 dB e -3 e -10 dB respectivamente, na faixa de frequência de operação. Estes valores são satisfatórios dado que o multiplicador será cascateverado a atenuadores para aplicação em sistemas.

A faixa de frequência obtida para 1 dB de ondulação no ganho de multiplicação foi 3.725 a 4.300 MHz, correspondendo a 14% de banda. Esta faixa de frequência pode ser deslocada para conter 3.700 MHz ajustando-se o comprimento da microlinha LT7.

Medindo-se o espectro de saída do quadruplicador verificou - se que a frequência fundamental, a segunda e a terceira harmônicas encontram-se 70 dBc abaixo da harmônica de saída, enquanto a quinta, sexta e oitava harmônicas estão respectivamente a -46 dBc, -48 dBc, -52 dBc e -25 dBc. Constatou-se assim boa pureza espectral, que pode ser aprimorada cascateverando - se um filtro passa-baixas na saída.

## CONCLUSÕES

Foi realizada uma investigação sobre a possibilidade de se construir um quaduplicador de frequências ativo de microondas para aplicação em sistemas de comunicação.

Através de considerações simples foram esboçadas as especificações mínimas do quaduplicador, e para atendê-las foi projetado um circuito composto por dois estágios dobradores a MESFET em cascata.

Foram aplicados resultados de análise não-linear no projeto dos dobradores de frequência, bem como nas discussões sobre a integração dos mesmos. O circuito projetado resultante é simples, de fácil ajuste, apresentando comportamento coerente com o previsto, validando a técnica de projeto.

Os resultados experimentais,  $10 \pm 0,5$  dB de ganho de multiplicação associado a potência de saída de + 10 dBm em 14% de banda de frequência, demonstraram a potencialidade da aplicação desse circuito em sistemas de comunicação.

O bom desempenho apresentado pelo quadruplicador de frequências ativo sugere o interesse de se realizar um estudo aprofundado sobre sua integração em sistemas, determinando-se suas especificações elétricas ótimas e realizando-se uma análise comparativa com quadruplicadores de frequências passivos.

## AGRADECIMENTOS

Os autores agradecem ao Sr. Jair Pereira de Souza pela colaboração na montagem e caracterização do protótipo do quadruplicador. Este trabalho foi realizado com o suporte financeiro do CPqD-TELEBRÁS.

## BIBLIOGRAFIA

- [1] - CAMARGO, E. e CORRERA, F.S. - "A high gain GaAs MESFET quadrupler", IEEE International Microwave Symp. Digest, pp 177-180, 1987.

- [2] - CAMARGO, E. - "Fenômenos não-lineares em transistores de efeito de campo de microondas e sua aplicação a multiplicadores de frequência", Tese de Doutorado, Escola Politécnica da USP, 1985.

- [3] - STRID, G. - "S-Parameters Simplify Accurate VCO Design", Microwaves, pg. 7.1-7.4, Maio, 1975.