# OTIMIZAÇÃO DE AMPLIFICADORES DE POTÊNCIA

## A TRANSISTORES MESFET

Uma publicação recente na literatura apresentou um método para determinar as regras de otimização de potência existentes para o projeto de um transistors baseado em MESFETs. O autor aplica este método para obter a saída de saída de grande sinal. Para obter a saída de saída de grande sinal, pode-se projetar um amplificador provisório que produza de saída a 1 dB de compressão e

Rodrigo Cordeiro Tupynambá

Sul América Teleinformática

Av. Indianópolis, 3435

04063 - São Paulo

Edmar Camargo

Laboratório de Microeletrônica

Escola Politécnica da USP

Cx Postal 8174 - 01051

São Paulo

## RESUMO

O objetivo do trabalho é demonstrar a aplicação de um método de otimização de amplificadores de potência para microondas, e de caracterização da sua impedância de saída em regime de grandes sinais. O primeiro circuito de teste foi realizado para operação em pequenos sinais, obtendo-se 12 dBm de potência de saída. O segundo circuito, otimizado para operação em potência apresentou 16 dBm de potência de saída.

## 1- INTRODUÇÃO

Um dos métodos mais empregados atualmente para o projeto de amplificadores de potência de microondas, consiste em medir a impedância de saída em grandes sinais pelos processos convencionais de "load pull" e considerar que a impedância de entrada é linear. Entretanto, esta forma de resolver o problema requer um tempo considerável em bancada para caracterização do componente.

Neste trabalho apresenta-se um método de projeto simples e rápido realizável através do emprego de programas de análise linear e de medidas estáticas e dinâmicas dos transistores MESFET. Além disso, o trabalho pretende contribuir na compreensão do comportamento da impedância de saída do transistor em função do nível de sinal e introduz uma forma prática de medi-la em regime de grandes sinais através do analisador de circuitos vetorial. Dois circuitos de teste foram construídos com o objetivo de demonstrar a aplicação do método.

## 2 - FUNDAMENTOS TEÓRICOS

Uma publicação recentemente introduzida na literatura<sup>2</sup>, apresentou uma formulação matemática para determinar as curvas de potência constante em função da carga de um transistor tipo MESFET. O método mostra uma carga ótima,  $R_{ot}$ , obtida a partir das curvas estáticas do transistor, que proporciona máxima excursão de tensão e corrente, portanto máxima potência de saída. Para outras cargas  $Z_L$ , a potência é proporcional a  $\text{Re}(Z_L)$  para  $|Z_L| < R_{ot}$  ou a  $\text{Re}(1/Z_L)$  para  $|Z_L| > R_{ot}$ . Assim, pode-se projetar um amplificador prevendo sua potência de saída a 1 dB de compressão do ganho.

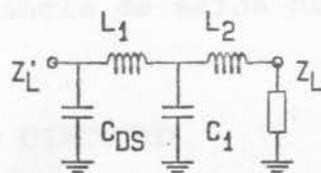

Essas relações simples são válidas apenas para a carga diretamente conectada ao gerador interno de corrente do transistor. No caso de transistores encapsulados, deve-se levar em conta a capacidade de dreno e as reatâncias parasitas da cápsula. Apresenta-se na figura 1, um modelo para o circuito de saída, que permite transformar a impedância de carga junto à fonte de corrente para o terminal externo da cápsula.

Fig 1. Circuito de Carga do transistor.

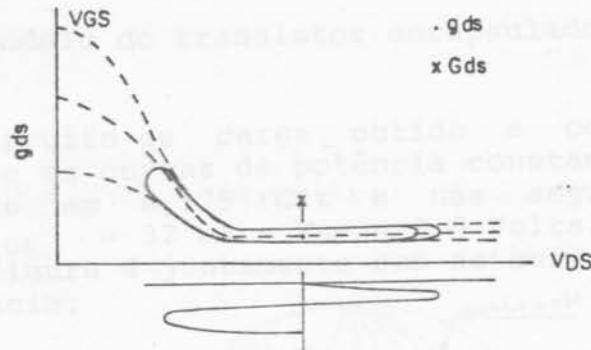

Uma vez projetado o circuito de saída, é interessante discutir qual a impedância de saída do amplificador, em regime de grandes sinais. Este parâmetro, no caso de amplificadores classe A depende essencialmente do comportamento da condutância de saída não-linear,  $g_{ds}$ . Esta hipótese já foi adotada por outros autores<sup>3</sup> e é válida para frequências em que as não-linearidades reativas não sejam importantes. A condutância de saída em função das tensões terminais está representada no diagrama da figura 2.

Assumindo uma reta de carga sobre as características estáticas  $I_{DS} \times V_{DS}$  verifica-se o estabelecimento de uma relação entre tensão de entrada e tensão de saída. Logo, a aplicação de um tensão dinâmica na entrada de grande amplitude, provoca na saída uma elevada excursão de tensão no dreno que modula  $g_{ds}$ . A condutância de saída equivalente de grandes sinais,  $G_{ds}$  na frequência fundamental, pode ser obtida através do cálculo da média de cada valor instantâneo em um ciclo, ou seja:

$$G_{ds} = (1/T) \int_0^T g_{ds}[V_1(t-\tau), V_2(t)] dt$$

Através da figura 2, verifica-se que  $G_{ds}$  aumenta com a amplitude da tensão de dreno ou seja a resistência de saída de pequenos sinais que é elevada, diminui melhorando a adaptação de saída. Logo, consegue-se que a impedância de saída do amplificador em regime de grandes sinais é função do descasamento entre a condutância de saída de grandes sinais e da condutância apresentada pelo circuito de carga.

Fig 2 - Condutância de saída não-linear.

### 3 - PROJETO DO CIRCUITO

O objetivo é projetar um circuito tal que permita investigar simultaneamente as condições de operação em regime de grandes e pequenos sinais. A banda de 5,9 a 6,4 GHz foi escolhida pela sua importância nos sistemas de comunicação brasileiros. O dispositivo escolhido para o projeto é do tipo NE72084, fabricado pela NEC que apresenta uma geometria de porta de  $1 \times 350 \mu\text{m}$  e uma potência de saída de 50 mW em 4 GHz.

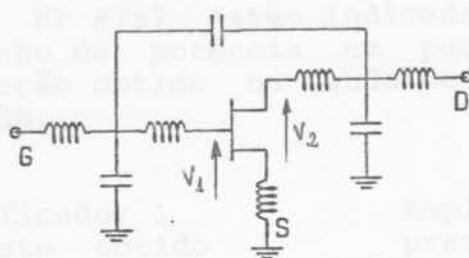

O projeto iniciou-se pela determinação da máxima corrente de dreno, em um traçador de curvas, obtendo-se  $I_{DSS} = 64 \text{ mA}$ . A máxima tensão de dreno  $V_{DS} = 5 \text{ volts}$ , foi obtida das especificações fornecidas pelo fabricante. Em seguida, empregando-se os parâmetros-S fornecidos pelo fabricante para os transistores em chip procurou-se modelar o transistor encapsulado representado na figura 3, através dos parâmetros-S para o transistor encapsulado, e do programa de análise linear TOUCHSTONE comercializado pela EESOF. Os parâmetros do circuito de saída obtido por este modelamento estão relacionados na tabela I.

$$\begin{array}{ll} C_{DS} = 0.017 \text{ pF} & C_1 = 0.15 \text{ pF} \\ L_1 = 0.45 \text{ nH} & L_2 = 0.35 \text{ nH} \end{array}$$

Tabela I - Parâmetros do circuito de saída.

Fig 3 - Modelo do transistor encapsulado.

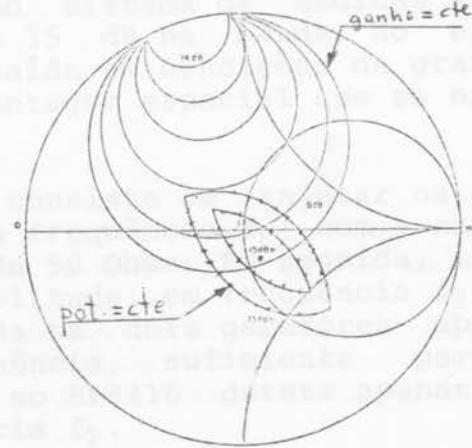

Com o circuito de carga obtido e com os parâmetros-S, determinaram-se as curvas de potência constante para o transistor medido operando em 6,175 GHz e nas seguintes condições de polarização:  $I_{DS} = 32 \text{ mA}$  e  $V_{DS} = 3,0 \text{ Volts}$ . Os resultados estão indicados na figura 4 juntamente com as curvas representativas do ganho de potência.

Fig 4 - Curvas de ganho e potência constante.

De acordo com o método proposto, a potência obtida será a máxima potência linear, e corresponde aproximadamente à potência para 1 dB de compressão do ganho. Para comprovar esta teoria, realizou-se o projeto de um amplificador para operar em duas situações distintas: 1) Com  $Z_L = 50 \text{ Ohms}$ , situação próxima à de máxima potência, com ganho esperado de 9,5 dB e potência de +14 dBm. O circuito de entrada deve prover o casamento conjugado da impedância de entrada resultante; 2) Na situação de máximo ganho na faixa de 500 MHz, com ganho esperado de 11.5 dB e uma potência de saída de +10 dBm. Ambos os projetos foram montados sobre um mesmo substrato flexível de  $\epsilon_r = 2.2$ , com ajustes que permitiram, na mesma montagem, o estudo de um ou de outro caso.

#### 4 - RESULTADOS EXPERIMENTAIS

Os dois circuitos foram caracterizados em termos de ganho e perdas de retorno na entrada e saída em condições de pequenos

e grandes sinais. Os resultados obtidos através do analisador de circuitos escalar HP 8757 estão indicados na tabela II. No caso particular do ganho de potência em pequenos sinais, deve-se ressaltar a variação obtida na banda de 5,9 a 6,4 GHz que é da ordem de  $-/+ 0.5$  dB.

|       | Amplificador 1 |          | Amplificador 2 |          |

|-------|----------------|----------|----------------|----------|

|       | previsto       | obtido   | previsto       | obtido   |

| ganho | 9,5 dB         | 9,0 dB   | 11,5 dB        | 10,0 dB  |

| P@1dB | 14,0 dBm       | 16,0 dBm | 10,0 dBm       | 12,0 dBm |

Tabela II - Resumo dos resultados experimentais.

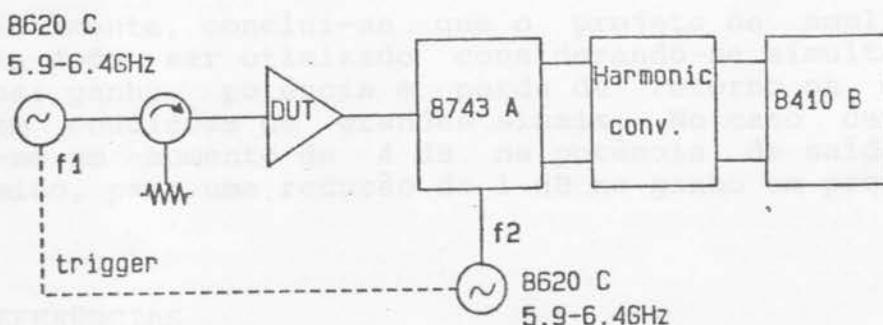

Na condição de grandes sinais, a perda de retorno na entrada foi obtida pelo mesmo sistema de medidas anterior, obtendo-se resultado melhor que 15 dB na banda. No entanto, a medida da perda de retorno na saída em condições de grandes sinais requereu o emprego de uma montagem especial que se encontra representada na figura 5.

O procedimento consiste em injetar na porta um sinal de amplitude elevada na frequência  $f_1$ , com a saída convenientemente terminada em carga de 50 Ohms. Em seguida, injeta-se na saída um sinal de pequena amplitude em frequência  $f_2$  próxima do sinal de entrada. Neste medida os dois geradores apresentam uma pequena diferença de frequência, suficiente para que o conversor harmônico associado ao HP8410 detete apenas o sinal de pequena amplitude na frequencia  $f_2$ .

Fig 5 - Medida da impedância em grandes sinais.

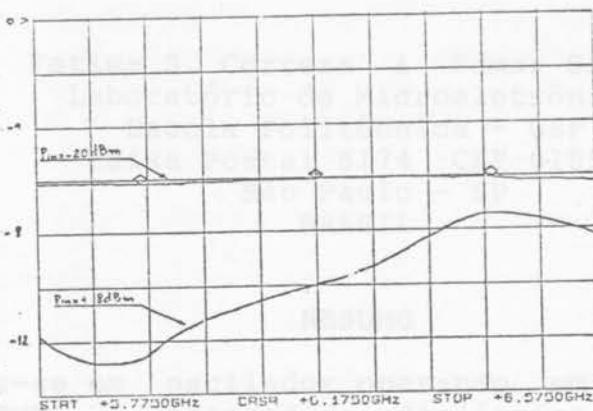

A perda de retorno de saída está representada na figura 6 para dois níveis de potência incidente. Em pequenos sinais verifica-se que ela é constante com a frequencia e é igual a 6 dB. Observa-se em grandes sinais uma melhoria do casamento, comprovando a previsão de variação da impedância de saída com aumento do nível de sinal. É interessante observar também que a compressão é maior em baixas freqüencias do que em altas, pela

diferença de variação da perda de retorno, 6,5 dB no extremo inferior contra 1,5 dB no extremo superior.

Fig 6 - Perda de retorno na saída.

## 5 - CONCLUSÕES

Em ambos os circuitos de teste obteve-se um ganho linear mais baixo que o esperado, o que indica que há uma discrepância entre os parâmetros-S típicos e aqueles da unidade em teste. A previsão para a potência de saída foi bastante satisfatória; 16 e 12 dBm para os amplificadores 1 e 2, respectivamente, contra uma previsão de 14 e 10 dBm. Verificou-se também que o máximo ganho está associado a uma boa perda de retorno desde que o transistor permaneça na região linear, ou seja haverá sempre um compromisso entre ganho e potência.

Finalmente, conclui-se que o projeto de amplificadores de potência pode ser otimizado considerando-se simultaneamente os aspectos: ganho, potência e perda de retorno na entrada e na saída em condições de grandes sinais. No caso deste trabalho, obteve-se um aumento de 4 dB na potência de saída com o ganho comprimido, para uma redução de 1 dB no ganho em pequenos sinais.

## REFERÊNCIAS

- 1 - F. N. Sechi & R. W. Paglione - "Design of a High-Gain FET Amplifier Operating at 4.4 - 5.0 GHz", IEEE Journal of Solid State Circuits, Vol 12, No 3, 1977.

- 2 - S. C. Cripps - "A Theory For The Prediction Of GaAs FET Load-Pull Power Counturs", 1983 MTT-S Int. Micro. Symp. Dig.

- 3 - C. Rauscher & H. A. Willing - "Design of Broad-Band GaAs FET power Amplifiers", IEEE Trans. on Micro. Theo. and Techniques, Vol 28, No 10, 1980.